在面向功率电子专业人士的网站上,如何导通 MOSFET 的话题可能不值一提,就好像在烹饪展上问如何把水烧开一样。毕竟这不应当是个大问题。与双极型器件不同,场效应晶体管是多数载流子器件(majority carrier device)。我们无需担心电流增益,定制基础电流以匹配 hfe 和可变集电极电流的极值,或者提供负压驱动。MOSFET 是电压驱动的,所以当把等于或大于阈值的电压施加到栅极时它们就会导通,是不是?这些假设有多么错误取决于何时发现错误。量产最后期限之前的时间通常只有几天。没有一例记载表明设计工程师在仿真期间发现了问题。

随着越来越多转换器采用数字控制,需要重新认识如何导通 MOSFET(或者在更基本层面,确定应当施加到栅极的最小电压)的问题。虽然数字控制可提供高一级的灵活性和功能性,但用于实现数字控制的 DSP、FPGA 和其他可编程器件在工作时使用的却是低电源电压。因此,有必要将最终 PWM 信号的电压提高到 MOSFET 栅极要求的水平。这时,由于对 MOSFET 导通的真正原因的错误认识,问题随之出现。许多数字设计工程师着眼于栅极阈值电压并得出结论:如同其数字逻辑一样,MOSFET 将在阈值被超过时立即改变状态。

表 I) SiR826ADP 的栅极阈值规范

首先,阈值电压 Vgsth 不是提供给系统工程师参考的。它是漏极电流超过 250 uA 阈值时的栅极电压,同时还是在实际应用中不会出现的条件下测得的。有些情况下,5V 或更高的固定 Vds可能会被当作测试条件,但通常是按规定在栅极和漏极一起短路时测量的。这一点无需深究,产品数据表中有明确规定。表I显示了针对 SiR826ADP 的 Vgsth 规范和测试条件。许多应用中都存在对所谓“诱发”栅极电压(例如在同步降压的低边 MOSFET中)的担心。同样,使栅极电压高于阈值并不会自动驱动器件进入由击穿诱发的失效状态。Vgsth 是 MOSFET 设计工程师的参数,它定义了器件处于导通阈值时的状态。它代表的是开始,离结束还很遥远。栅极电压在关断状态时应低于阈值,以最小化漏电流。但在导通状态期间,系统设计工程师能够并应当完全忽略之。

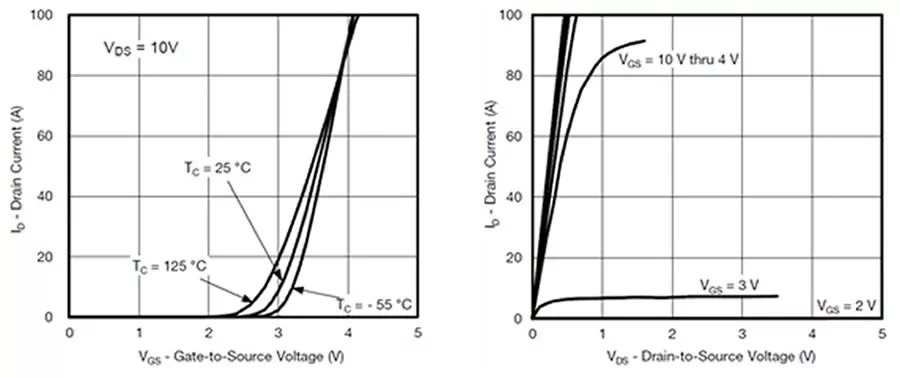

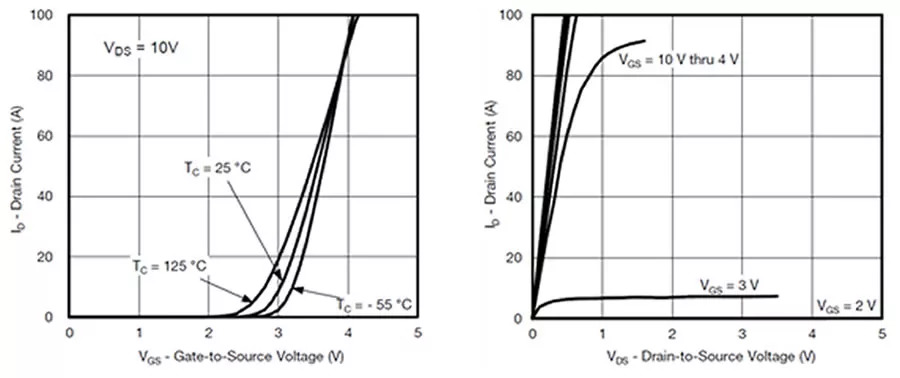

产品数据表提供的另一个曲线是指 MOSFET 导通伴随着栅极电压增加(转移特性)。图1 显示的是 SiR826ADP 的该曲线。但转移特性更多的是电流变化关于温度和所施加栅极电压的度量。Vds 保持恒定但处于高水平,有时高达 15 V,但产品数据表并不总是提供这个参数。在下面所示的曲线中,20 A ld 电流, 3.2 V 的门极驱动电压是不够的。该组合会保持 10 V 的典型 Vds 和 200 W 的连续功率耗散。转移曲线在 MOSFET 在线性模式下工作时十分重要,但与开关操作并无多大关系。

图1) SiR826ADP 的转移特性 图2) SiR826ADP 的输出特性

包含 MOSFET 完全导通时的数据的曲线称为输出特性曲线(如图2 所示)。这里,对于不同的 Vgs 值,MOSFET 的正向压降是电流的函数。设计工程师可参考该曲线来确保栅极电压是足够的。对于可保证 RDS(on) 的每个栅极电压,都存在一个电压范围,在此范围内,Vds 下降与电流保持严格线性关系(从零开始)。对于低于该范围的栅极电压值,随着电流增加,曲线不再是线性的,在经过拐点后平坦化。图3 显示了栅极电压为 2.5 V ~ 3.6 V 时的详细输出特性。MOSFET 用户通常将此视为线性模式。但器件设计工程师将灰色区域称为电流饱和区——对于给定的栅极电压,可以提供的电流达到其饱和极限。所施加 Vds 的任何增加将在电流仅有轻微增加的情况下持续,而即使电流的微小改变也会导致 Vds 的相对大幅增加。对于较高栅极电压,当 MOSFET 完全导通时,任何工作点都将位于左侧绿色区域,该区域被标记为电阻(欧姆)区。请注意,所有曲线都是典型情况,没有最小或最大限值,并且是在 25℃ 下得到的。在更低温度下,使器件处于电阻区需要的栅极电压会更高,增速为 0.3 %/℃。

图3) 扩展输出特性图 图4) 栅极电荷特性

在面对输出特性时,设计工程师总需要知道其特定工作条件下的 RDS(on) ,通常这是在 VGS 和 Ids 组合条件下,这时曲线偏离直而细的绿色区,进入灰色区域。例如,在上面的例子中,这可能为栅极电压 VGS = 3.1 V 和 10 A 启动电流的组合。他们知道 RDS(on) 将高于规范值,但 MOSFET 制造商会对此提供一个大概说明吗?由于 Vds 和 Ids都可从曲线得到,那么就存在将二者相除,以得到“有效” RDS(on) 的想法,而且实际上往往就是这样做的。但遗憾的是这里并无 RDS(on) 可供计算,其在给定条件下并不存在。负载线代表电阻的任何部分必须以线性方式穿过原点。我们当然能够将完整负载线模拟为非线性电阻。如果不出意外,这将确保对实际行为的任何理解在原点 ( 0,0 ) 处得到保持。

图4 所示的栅极电荷曲线提供了导通 MOSFET 的真正线索。虽然每个 MOSFET 都会提供该曲线,但设计工程师并不总是理解其含义。此外,MOSFET 技术的最新进展(如沟槽和屏蔽栅极以及电荷补偿超级结结构)要求对此信息有新的认知。首先,“栅极电荷”这个词本身有一定误导作用。线性和分段的曲线看上去并不像任何电容的充电电压,无论其值有多么非线性。在现实中,栅极电荷曲线实际上代表不是并联、具有不同容值和承载不同电压的两个电容的叠加。在文献中,有效容值(从栅极引出线看)的定义是:Ciss =Cgs +Cgd。

虽然这是一个便于测量并在产品数据表中加以规定的实体,但值得注意的是 Ciss 并非物理电容。认为只需给“栅极电容 Ciss”施加电压即可使MSOFET导通的观念是错误的。 如图5 所示,在栅极导通前,源电容 Cgs 未充电,但栅漏电容 Cgd 具有需要消除的负电压/电荷。两个电容都是非线性的,其值会相对于所施加的电压而有很大差异。因此,开关特性更多取决于其储存的电荷而非任意给定电压下的容值。

图5) 带有初始电压的栅极电容图 6) 简化的电感式导通电路

由于构成 Ciss 的两个组成电容具有物理差异且充电至不同的电压,所以导通过程也有两个阶段。电感性和电阻性负载的准确顺序是不同的;但在大多数实际应用中,负载大部分为电感负载并能使用图6 所示的简单电路来描述。关于时序图 图7:

T0 – T1 :Cgs 从零充电至 Vgsth 。Vds 或 Ids无变化。

T1 – T2 :器件中的电流随着栅极电压从 Vgsth 上升至平台电压 Vgp 而开始上升。Ids 从 0 A 上升至满负载电流,但 Vds 无变化。相关电荷量是 Cgs 从 0 V 到 Vgp 的积分,在产品数据表中以 Qgs 表示。

|