|

|

|

|

| |  |  | | | | | | 呵呵不是打酱油是为了在您的帖子中留个记号,有跟新好提醒。 |

|

|

|

|

|  | | | | 电感设计成DCM,如果是同步续流的,电路会工作在临界模式吧。

1.上管应该是零电流开启,硬关断。

2.下管是零压开启(因为二极管在死区时间已经先续流),零电流关断。

3.DCM的话,电感体积相对会大些,而且电感损耗也将占更重比例。换句话说,就是管子是舒服点了,但电感吃力了。

4.同样,输入和输出端的电容也吃力了。 |

|

|

|  |  | | | | | 怎么会工作在临界模式呢?前面都说了,电流是可以反向流动的。事实上,同步整流根本不存在DCM。

举一个最极端的例子:负载电流为零。分析了负载电流为零的例子就明白同步BUCK是怎样工作的了。

1.上管应该是零电流开启,硬关断。

这个结论显然是错误的,按照顶楼的设定,在下管关断前,电感电流的数值肯定是一个负值。那么在死去时间,上管寄生二极管将为电感续流。

3.DCM的话,电感体积相对会大些,而且电感损耗也将占更重比例。换句话说,就是管子是舒服点了,但电感吃力了。

电感损耗有可能是我的这个设想中,最难解决的部分。铜损增加基本上是肯定的,铁损看起来似乎也会加大(因为推导出DCM模式下,线圈圈数和Bmax无关,这儿没经过推导都不敢确定了)

4.同样,输入和输出端的电容也吃力了。

这的确有可能成为问题,但如果是多相电路呢? |

|

|

| |  |  | | | | | | 哦,是电流向下走了,那这样下管也是硬关断。

但电流还是在不停的变化,不会回到0电流时停一断时间。从电流波形上看,还是上升下降的三角波,不是间断的三角波。 |

|

|

| | |  |  | | | | | | | 汗!

麻烦你推导一下,当输出电流为零的时候,工作状态如何。

可以考虑固定占空比,开环工作,比如占空比为0.5。

为了简单起见,还可以假设没有死区,反正是理论分析,越简单越好。 |

|

|

|

|

|

| | | |  |  | | | | | | | | 不能全程软开关,感觉效率还是不怎么样的。

再加上电感和电容都更吃力了。 |

|

|

| | | | |  |  | | | | | | | | | MOSFET关断损耗相对较小,不是主要矛盾。

实际上,我设计的这种工作方式,MOSFET的工作状态和LLC是一样的。

我之所以想到这东西,就是因为正在做的一个东西里面既有LLC,又有同步BUCK,加上这儿讨论到同步BUCK(或同步boost)存在续流管寄生二极管的反向恢复问题。考虑两者的差异,我想除了这么一个可能的方法。

电感问题肯定无解,电容问题如果在多相同步BUCK中就没那么严重了,说不定不比按CCM模式设计的同步BUCK交流电流大也不是不可能的。 |

|

|

| | | | | |  |  | | | | | | | | | | 开通的关断损耗其实是差不多的,只是开通是多了一个结电容上存的电量而以。

但低压时这个结电容上的电量并没有高压时那样可观。

上面之所以误把它说成临界模式,是因为电感的纹波电流和电容的纹波电流和临界模式相当。或者说,用临界模式来计算更能贴近实际。 |

|

|

|  | | | | 损耗肯定会大的:

1、CCM损耗为:上管开关损耗+双管导通损耗+电感铁损+电感铜损+输入出电容ESR损耗。

2、DCM模式损耗:上管关断损耗+下管关断损耗+双管导通损耗+电感铁损+电感铜损+输入出电容ESR损耗+输入电源充电损耗。

3、其中近似:“上管开关损耗=上管关断损耗+下管关断损耗”;

4、电感铁损由单向变为双向,单向ΔB大比率上升,损耗虽然没有定量的计算,但可以想象非常的高。

5、电感铜损增加4倍以上,双管导通损耗4倍以上

6、ESR损耗增加4倍以上,并增加了充电转换效率损耗

7、由于电感需要被输出滤波电容反向充电,所以输出电压纹波增大并很难减小。控制电路相应会比较复杂,因为电压反馈无法及时得到相应,动态响应变差,会出现低频大幅度纹波(电感电流不能突变,所以电压反馈不能及时的反映到输出网络上) |

|

|

|  |  | | | | |

你的这些数据怎么来的?和无穷大电感做对比吗?

没有经过试验,也没有经过计算,你的结论未必太轻率了。

起码,你忽略一个问题:续流管的反向恢复损耗,这在按CCM设计的同步BUCK中肯定存在,通过集成肖特基二极管可以减轻这个问题,但无法消除。

如果我的办法可行,那么完全可以不用集成肖特基二极管的MOSFET。当然如果两者价格没有明显差异,那么不用集成肖特基二极管的MOSFET意义不大。 |

|

|

| |  |  | | | | | | 基本的估算还是有的。这估算是建立在你认为电流是双向的,如果是临界的,这个估算就不对了。当然临界不容易,因为负载是变化的,所以平均应该是双向的。

所以:

1、开关损耗。这个没啥异议吧?在双向电流作用下,虽然两个管子的都是零开启,但关断的时候,电压和电流都不为零。我近似开关损耗不变其实还是宽松了。

2、电感的铁损没啥异议吧?铁损是磁滞回线包围的面积,工作于DCM模式,铁损比CCM大很多,尤其是功率要和CCM一样的情况下。而且你这个是双向的回线,铁损比一般的DCM还要大两倍。

3、DCM的电流是不是CCM的两倍没算过,近似为两倍的话,所有的电阻性损耗都要增加4倍,这没错吧?

4、反向充电的损耗不好估算,和电源的种类有关,如果电源是蓄电池的话损耗就很大了。 |

|

|

|

|

| | | | |  |  | | | | | | | | | 上面说过,同步互补的方式,电感纹波电流和临界模式一样,是连续的三角波,这样铁损也就和临界模式相当。

而临界模式的铁损,应该不会比DCM模式大很多吧。 |

|

|

| | |  |  | | | | | | | 首先,如果按通常的设计,你不会考虑电感量越大越好对吧?

一般怎么考虑?di设为多少?输出电流的一半?三分之一?

根据公式:ΔB=U·Ton/NP·Ae,如果直接通过减少线圈圈数来减小电感量,的确会造成ΔB增大,铁损增大。

但另一方面,线圈圈数减少,相应的铜线长度变短,铜损减小。线圈圈数减少之后,同样的窗口面积也允许绕更多的铜线,用以增大导线的有效截面积,进一步减少铜损。

另一方面,如果不改变线圈的圈数,通过调整气隙长度来调整电感量,那么ΔB不变,铁损不会改变。不过由于电流有效值增加,铜损会增加。

要按最小功耗来设计,显然需要在减小线圈圈数的同时,调整气隙长度,以得到最佳参数,这是优化设计的问题了。要知道最终电感损耗能增加多少,首先要知道作为对比的电感参数。

开通损耗肯定减少,关断损耗肯定增加。但消除了寄生二极管的反向恢复损耗,这部分能量损耗肯定是减少的。 |

|

|

| | | |  |  | | | | | | | | 1、通过增加气息的方法让ΔB不变是在CCM模式下,DCM模式ΔB能不变吗?

2、L和N平方正比,和储能一次方正比,也就是说你降低一倍的感量也即电感变为原来的二分之一,圈数只能减小1.414倍,电阻并不能减小一倍,也不能让你的铜加粗一倍。当然如果是临界模式,电流也不需要增加一倍。

3、但是要是非临界模式,下管导通期间输出电容要给电感反向充电,因此为了补偿这部分能量,实际上电流可能不止两倍CCM电流。

4、反向恢复貌似是没了,综合起来的损耗确实需要仔细算算。 |

|

|

| | | | |  |  | | | | | | | | | 1. 对于同步buck不存在DCM,我只是借用DCM的电感设计。你考虑一下输出电流为零的情况就明白了。

2. 电感降低一半,的确匝数是变成了0.707倍。这是不是意味着铜线面积可以增加到原来的1.414呢?如果不计趋肤效应的影响,那么电阻是不是变成了一半?

3. 这儿要谈多少倍,首先要考虑作比较用的CCM模式的原始电路的纹波电流。

至于电容电流,我的考虑是不是这个方案更适合多相电路,同步多相电路中,各分支的交流电流是可以互相抵消的。如果是单相电路,为了避免电容损耗过大,设法减小电容的ESR是必须要考虑的。 |

|

|

| | | | | |  |  | | | | | | | | | | 我觉得这事儿不面谈根本说不清楚,我说的DCM也不是Boost的DCM。这个设计类似于一个振荡器的设计了,电流在初级次级之间震荡,电感上的电流是正负两个方向的。 |

|

|

| | | | | | |  |  | | | | | | | | | | | 电流来回流动的BUCK电路其实变成了另一个东西了:丁类放大器,你想想丁类放大器的工作就明白了。 |

|

|

| | | | | | | |  |  | | | | | | | | | | | | 丁类放大器咱不熟,但是知道你让功率电感工作在震荡模式下一定是高损耗的。 |

|

|

| | | | | | | | |  |  | | | | | | | | | | | | | 这儿也不是真正的震荡,不过损耗是必然的。

其实问题不在于是否有损耗,而在于增加的损耗和减少的损耗到底哪一个多。 |

|

|

|

| | | | | | | | | | |  |  | | | | | | | | | | | | | | | 反向恢复的损耗是多少?这个问题不弄清楚就难以估算。

特别是没有内部寄生二极管是快恢复类型的MOSFET时,反向恢复问题更严重。 |

|

|

|

| | | | | | | | | | | | |  |  | | | | | | | | | | | | | | | | | 这儿怎么处理?

工程问题本来就是一个妥协的过程,解决一个问题往往引入新问题,完全只有优点没有缺点的方案几乎就不存在。 |

|

|

| | | | | | | | | | | | | |  |  | | | | | | | | | | | | | | | | | | 是啊,工程问题总是引入新的问题解决老的问题。这就是创新,但是你引入的损耗比原来的更加难以解决。我们有很多帖子都在讨论如何解决反向恢复损耗,你这个帖子也算一种创新想法,但是有很多问题要去解决,只有你解决了这些问题,才是真正的创新。

我觉得你可以继续想下去,思考总是好的,至少比那些因循守旧好,更比那些完全拿来的好。 |

|

|

| | | | | | | | | | | | | | |  |  | | | | | | | | | | | | | | | | | | | 没错,我这个主意就是要避开反向恢复。

至于减小MOSFET的开启损耗还是其次,可以算是附带的好处。这个附带的好处对于输入电压高的时候可能意义比较大一些。

另外,似乎内部附带肖特基二极管的MOSFET耐压都不是很高。

这个问题也容易理解,根据二极管的伏安特性公式,可知要能够尽量分流原有寄生二极管的的电流,则意味着需要较低的VF。而VF较低,则意味着漏电流较大,这对高压二极管来说是比较要命的。 |

|

|

| | | | | | | | | | | | | | | |  |  | | | | | | | | | | | | | | | | | | | | 呵呵,往往创新的目标最后变得不重要。有句话:有心栽花。。。无心插柳 |

|

|

|  |  | | | | | CCM模式少了体二极管的反向恢复损耗,还有电感小的话动态负载响应是更好吧? |

|

|

| |  |  | | | | | | 这个设想的初衷就在于零电压开启MOSFET,消除体二极管的反向恢复是零电压开启自然地好处,也是这个设想的初衷。

电感小,动态特性好算是你新给这个设想找到的一个好处。 |

|

|

|  | | | | 高电压小电流还凑合,低压大电流根本不可能嘛。假定12V转3.3V/25A(单相,4相交错出100A),如果CCM,电感峰值电流32.5A,纹波电流15A是没问题的;如果DCM的话,电感峰值(纹波)电流50A。效率先放一边,如果开关频率不变,等负载条件占空比也不变,50A/dt和15A/dt差了3倍多,干扰超强,EMI玩死人。。。

回头估算效率,上管:开通损耗小了,关断损耗不变;下管:开通损耗不变,关断损耗没了;导通损耗大了(平均电流一样,三角波电流有效值大于梯形波,以上面的数据为例,32.5A梯形波电流有效值为25.4*(D^0.5),50A三角波有效值为28.8* (D^0.5),电流有效值增大1.13倍,如果为临界模式则导通损耗增大1.28倍);输出电容损耗大了;电感损耗不变则需要增大体积,体积不变则会增加涡流损耗,铜损视窗口面积可能变大或不变。对比:减小了上管开通损耗并消除了下管关断损耗,增加了其他一堆损耗,应该是得不偿失的。。。 |

|

|

|  |  | | | | | 我这个设想究竟有没有用;或者什么情况下有用,什么情况下没有用——我自己也不知道。

我只是想到这个可能性,于是拿出来给大家讨论,也算活跃论坛了。

纹波电流增大,的确可能给EMI问题带来很大的压力。

至于效率,似乎还需要更进一步的分析才行,楼上的结论应该是得不偿失的也只是一种直觉,说服力还不够啊。 |

|

|

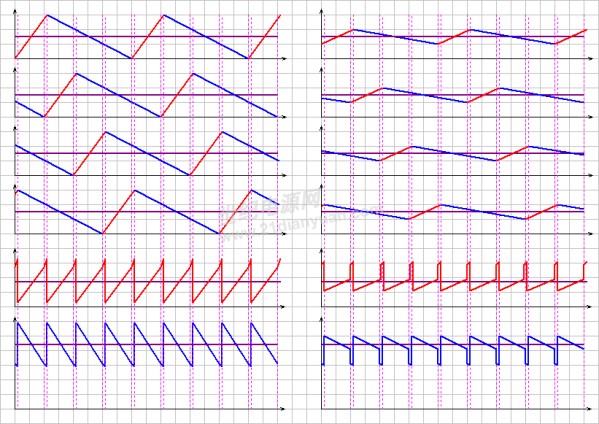

|  |  | | | | |

这是楼上说的12V输入,3.3V输出时,两种模式的电流波形示意图。对应的占空比D=0.275。

左边是临界模式的电流波形,对于我所定义的变换器,这对应着最大输出电流。右边是常规的设计发难,纹波电流峰值按最大输出电流的三分之一设计,在输出最大电流时的电流波形。

从上到下,1~4分别是四相的电感电流波形,波形中红色线段代表上管电流,蓝色为下管电流波形。最下面两个波形分别是输入电流和输出电流波形,其纹波部分对应着输入电容和输出电容电流。

从图中可以看出,输入电容、输出电容的纹波电流和常规设计差异并没有想象的那么大。 |

|

|

|

|

| | |  |  | | | | | | | 大致看了一下,没看明白,E文半白痴。

结论如何,能讲讲吗? |

|

|

| |  |  | | | | | | 跟据上图看来

DCM上管关断峰值大,下管开通峰值大,损耗是I平方R,虽上管开通与下管关断损耗小,但电流大时候的平方是倍数关系了,综合比CCM损耗不会小

如果仅仅是让下管二极管零关,你在其两端并联肖特基就可以了

峰值电流大得用更大参数的管子,驱动速度也会慢些

纹波电流的增大,需要更多的滤波成本,不管是不是想象中那么大

如果你想和LLC一样,得在主电路产生个与开关频率一样的谐振,让管子完全工作在零开零关 |

|

|

|

|

|

|

|

|

| | | |  |  | | | | | | | | 比较一种中心抽头的拓扑和Current Doubler拓扑,希望你选择Current Doubler拓扑时能明确的意识到自己要面对什么。

然后列了一张表,指出这两者之间每个器件上的电流个功率。 |

|

|

|  | | | | 这种方式很早就做实验试过,难度在续流管有很小的反向电流时关断(即输出电容向电感放电),这个小的反向电流很难取样 |

|

|

|  |  | | | | | 没看明白你的意思。

反向电流是肯定存在的,而且也是这种方案所必需的。

我猜想,你是不是说反向电流太小的时候有问题? |

|

|

| |  |  | | | | | | 看的人不少,怎么都不发表意见呢?

这会儿没空,有空画画不同模式的波形图 |

|

|

|

| | | |  |  | | | | | | | | 呵呵,我的目的就是给大家讨论讨论,否则我就做实际电路来做实验了。

这玩意儿仿真恐怕都难有结论。 |

|

|

| | | | |  |  | | | | | | | | | 这么复杂的事儿你也拿来讨论?论坛上大多只会讨论局部电路,或者基本原理,你让大家讨论这么纷繁复杂,前后纠缠,每个地方都需要精确计算的东西。

真的是服了你了! |

|

|

| | | | | |  |  | | | | | | | | | | 我不过是刚好想到了,而短时间之内也不可能自己做试验,所以拿出来讨论了。

其实,我第一次想到这个主意的时候,就在帖子上发言——想到就说的,那个帖子还被你批驳了,你大概还有印象吧? |

|

|

|

| | | | | | | |  |  | | | | | | | | | | | | 就是那个上管误导通的帖子里面,好像他的问题还没解决呢。 |

|

|

|

| | | | | | |  |  | | | | | | | | | | | 之前做过类似的尝试。这种方式最适合的是mutil-phase-CRM-BUCK。不过由于频率不固定导致需要进行协调才能很好同步多路输出以抑制输出电流波动。

对于给定的原件偏差,只能够调节每通道的出力不同而达到相位同步的目的。实际上就是滞环电流控制。

实际控制起来会很麻烦。

ps:似乎变频控制的拓扑都有不易多相问题? |

|

|

| | | | | | | |  |  | | | | | | | | | | | | 多相调频,又近了一步哈。通过调频,可以使电感峰值电流始终接近最佳值,避免了输出电流小的时候效率过低的问题。

变频多相的同步问题肯定比较麻烦,除非有专门设计的控制器。

或许,数字电源是个办法? |

|

|

| | | | | | | | |  |  | | | | | | | | | | | | | 高速比较器+CPLD+DA。

dsPIC和Picolo都没有合适的输出单元来做这个。 |

|

|

|

|

| | | | | | | | | | | |  |  | | | | | | | | | | | | | | | | CPLD或者FPGA肯定少不了,否则输出没办法解决。 |

|

|

| | | | | | | | | | | | |  |  | | | | | | | | | | | | | | | | | CPLD即可。FPGA配置芯片是外置的。也可以用个mcu来做fpga的配置。不过实在太占地方。要是这么干,boss要杀人的。 |

|

|

|

| |  |  | | | | | | 我的意思是说反向电流只需很小,能使上管零电压导通即可,反向电流大了损耗就大了,这么小的反向电流不好控制的 |

|

|

| | |  |  | | | | | | | 明白了!

不过也没必要过分追求这个电流有多小吧?

假设平均电流1A,那么反向电流0.1A和0.01A的损耗其实差别不大,对应的峰值电流分别是1.1A和1.01A,因为波形相同,有效值电流也是同样的比例,两者的损耗大约差18%,在总损耗中差别并不太大。

而且,反向电流稍大一点,可以保证反向电流持续一定的时间,这样有利于保证下管的寄生二极管在下管导通期间完成内部少数载流子的复合,彻底避免出现反向恢复电流。 |

|

|

|

| | | |  |  | | | | | | | | 但是你无法避免铁损变高的问题,在高频情况下尤为明显。损耗实际上发生了迁移,即开关损耗变成矫顽损耗。

需要计算,大电流情况下,铁损和开关损耗之间的转换比例。 |

|

|

| | | | |  |  | | | | | | | | | 在高频电流不大的情况下(输出电压高、电流不大)是有利的,其他情况需要测试数据。并不是简单的迁移。 |

|

|

|

|  | | | | 我做过了,只要准确检测好零电流就可以了,正如楼主所说,优点明显!下管选好一点比二极管发热低很多,下管零电流截止、零电压开通(体二极管先开通),上管零电压开通(稍作处理),接近理想了!有兴趣的多多交流 |

|

|

|  |  | | | | | 说明一下,我做的是输入400V,输出约100V、1A,所以上管是近似零电压开通,但是下管是非常接近零电压开通、零电流截止,主要是为了克服续流二极管Vf高的损耗以及反向恢复时间,对于输出高电压、电流不是很大的情况还是值得的。 |

|

|

| |  |  | | | | | | 终于有明确的说法:高压小电流的时候,这种方案是有益的。

多谢支持  |

|

|

| | |  |  | | | | | | | 你爽了吧,哈哈。

其实我前面就是质疑你大电流的情况  |

|

|

|

| |  |  | | | | | | 这个很不错,实例支撑。

低压大电流要是有人搞出来了,希望前来指教啊。 |

|

|

|  | | | | 除了前面所说的优点,此电路另一最主要优点就是利用MOS的低内阻(低压降),降低损耗,因为没有大于200V的肖特基,普通开关二极管1.2~1.5V的正向压降是死的,决定了功耗不可能再降低,而选用低Rds的MOSFET是可以把压降控制到0.nV的,具体要权衡性能和成本。低压大电流(10A以上)的情况,由于可以用肖特基,此时可能主要考虑的就是Iac导致的铁损了,不过具体我没有做过这么大电流的。 |

|

|

|  |  | | | | | SiC的肖特基二极管就有600和1200的。

肖特基只是一种二极管构成形式,而非材料。不同材料所制成的半导体器件差异会很大。 |

|

|

| |  |  | | | | | | 肖特基二极管真有600V的高压,那我可能是白混了。或许太久没关注器件的发展 |

|

|

| |  |  | | | | | | 碳化硅肖特基二极管正向压降可不低,甚至有超过两伏的。

事实上,正向压降基本上只取决于反向漏电电流。为了避免漏电流过大,高压二极管正向压降不可能太低了。 |

|

|

| |  |  | | | | | | SiC的Vf比普通快速二极管还要高,SiC的主要优点是反向恢复时间小,在CCM模式下是有些改善,但对DCM模式基本没有改善 |

|

|

|

|

|

|

| | |  |  | | | | | | | 你有没有考虑过这个问题:

对于同步BUCK,为了避免两只晶体管直通,必然会有死区时间,在死区时间内,两只晶体管都是关断的。

当低端晶体管(代替续流二极管那只晶体管)关断之后,因为高端晶体管(既普通BUCK变换器的主开关管)还没有开启,而电流不能中断,根据工作条件可知电流必然从低端晶体管内部寄生二极管流过。

当高端晶体管开启的时候,低端晶体管漏极电压被迅速拉高。由于在此前低端晶体管寄生二极管处于导通状态,当其电压被反偏的时候必然出现反向恢复过程。

我要问的是:你知道这个反向恢复过程导致的损耗是多少?

特别是当没有集成快恢复寄生二极管的MOSFET,你知道这种反向恢复过程可能导致MOSFET损坏吗? |

|

|

| | | |  |  | | | | | | | | 仅仅是为了抑制反向恢复,有点儿得不偿失。但是,小电流确实有他的好处。 |

|

|

| | | | |  |  | | | | | | | | | 其实,这种设想是否适用并不重要,重要的是思考,如果思考的结果能有所得当然最好,没有也不必失望。

思考的本身比成果更重要!

如果我们没有了自己的思考,那么我们就不再是工程师,只是一帮匠人。 |

|

|

|

| | | | | |  |  | | | | | | | | | | 论坛现在有个超级吵架贴,按你的性格应该按捺不住就冲进去了,咋没看见你的身影啊。 |

|

|

|

| | | | |  |  | | | | | | | | | 再说,为了避免(不是抑制,是彻底避免)反向恢复并不见得是得不偿失,只不过现在有更好的方法来解决问题:比如低电压MOSFET有内部并联肖特基二极管的MOSFET;高压则有把通过参入金等杂质来减低载流子存储寿命,以降低寄生二极管的反向恢复时间。

所以现在做同步BUCK,反向恢复问题不那么严重了,起码基本上能保证器件不会因此而损坏。

昨晚我看了一个帖子,里面是某公司的一个应用文档,讲LLC中晶体管失效模型,其中一个原因就是在启动的时候,出现了反向恢复问题(稳态时LLC是不存在反向恢复问题的)。反向恢复问题本身到不至于损坏晶体管,但如果反向恢复电流过大,则可能导致内部寄生三极管导通——这时候可能出现局部二次击穿,出现二次击穿则晶体管将会由于热点温度过高而损坏。 |

|

|

| | | |  |  | | | | | | | | 一般的同步mos的反向恢复时间也就30ns左右啊,这个损耗难道比增加的导通损耗大? |

|

|

| | | | |  |  | | | | | | | | | 汗!你说的什么管子?

如果是最普通的,没有特别优化的MOSFET,那么寄生二极管的反向恢复时间大约是数百ns。

实际上,反向恢复实际上是电流还不是最大的问题。更大的问题是反向恢复电流有可能导致寄生三极管出现二次击穿——这儿所说的寄生三极管基极和发射级是用金属连接在一起的,所以通常不会起任何作用。但当反向恢复电流很大时,流过短路基极、发射级的金属时,有可能在金属上产生足够的压降,导致三极管导通,这就出现了三级管二次击穿的可能,而高端晶体管开通产生的很大的dv/dt,又为三极管二次击穿创造了条件。 |

|

|

|

| | | | | |  |  | | | | | | | | | | 低压mos一般都是这个水平啊,刚才查了一下IR ST VISHAY的,一般的都是典型值在50ns的水平。 |

|

|

| | | | | | |  |  | | | | | | | | | | | 是内部并联了肖特基二极管的吧?你找找早期生产的MOSFET的资料看看。 |

|

|

| | | | | |  |  | | | | | | | | | | 二次击穿是个问题,哪怕恢复时间很短,如果上管开通过快,这个短路电流造成的压降也会使寄生三极管导通。 |

|

|

| | | | | | |  |  | | | | | | | | | | | 上管零电压开通、下管零电流关断、下管正向压降低是其最大优点!这些不都是理想状态吗? |

|

|

|

|

|  | | | | 你这个方式1998年国外已经有论文做过了,几路交错并联用在芯片电源里了。以后有新想法先查资料哦 |

|

|

|

|  |  | | | | | 多谢指教。

当初只不过思考中有所得给大家分享一下而已,所以查新没什么必要吧?

我又没打算把这个想法拿来申请专利什么的。

不过,既然国外早就有这样的做法,算是所见略同吧。说明我这个想法还是靠谱的,不是个愚蠢的想法。

|

|

|